안녕하세요

트랜지스터(Transistor)는 전기적 신호의 증폭, 흐름의 도통과 차단에 있어서

아주 효과적인 specification(사양)을 가지고 있기 때문에

현대 반도체 회로에서 쓰이지 않는 곳이 없을 정도로 전자 회로에서 필수적인 요소로써 자리매김해 왔습니다.

이러한 transistor들 중 현대에서 가장 많이 쓰이는 대표적인 두 개가 바로

BJT(Bipolar Junction Transistor) 과 MOSFET(Metal-Oxide-Semiconductor Field Effect Transistor) 입니다.

BJT는 Carrier로 전자와 정공을 둘다 사용하는 양극성 전류 구동원입니다.

그리고

MOSFET은 Carrier로 전자 또는 정공 하나만을 사용하는 단극성 전압 제어 장치 입니다.

BJT는 구조가 단순하며 양극성이라는 특성으로 인하여 다양한 기능을 소화할 수 있지만

전력 소모가 크고, 특히 상대적으로 큰 layout area를 가지고 있습니다.

이는 현대 미세 반도체 공정에 있어서

chip의 density(집적도)를 향상시키는 부분에서 큰 disadvantage로 작용합니다.

이로 인하여 대부분의 반도체 미세 공정과 회로 설계에서는 BJT가 아닌 MOSFET을 사용하고 있습니다.

그러므로 우리는 MOSFET을 중점적으로 다루게 될 것입니다.

이번 글에서는 본격적으로 MOSFET 소자를 사용한 Amplifier(증폭기) 회로에 대해서 알아보겠습니다.

증폭기는 간단하기 input에 들어가는 신호의 전력을 증폭시켜 output으로 내보내는 device 입니다.

이러한 특성을 가진 증폭기는

신호의 증폭 뿐만이 아니라 낮은 전력 소모를 위해 다양한 회로에서 필수적으로 사용되고 있습니다.

그렇다면 MOSFET을 사용한 다양한 amp circuit을 배우기 전에

맛보기로 가장 많이 사용되는 MOSFET 증폭기인 CS amp의 구조를 간단히 분석해 보겠습니다.

Common Source Amplifier circuit(CS-Amp)는

Source 단자를 Common 단자로 하는 MOSFET 증폭기를 의미합니다.

CS 증폭기의 동작 과정은 다음과 같습니다.

Gate 단자에 입력 신호를 인가해준다면 Source와 Drain 사이에 channel이 생겨 전류가 흐르게 되고,

흐르는 전류는 Drain 단자의 저항 R(D)에 의해 전압으로 변환 됩니다.

최종적으로 변환된 전압은 Drain 단자에 있는 output node로 출력됩니다.

이러한 과정을 거치는 CS 증폭기의 입력-출력 전압 변화는

오른쪽의 VTC(Voltage Transfer Characteristic) graph와 같이 나타낼 수 있습니다.

VTC(Voltage Transfer Characteristic) graph는 입력 v(GS)와 출력 v(DS)의 변화 양상을 나타낸 그래프 입니다.

그렇게 때문에 VTC 그래프를 통해서 입-출력 전압에 따른 MOSFET의 동작 영역을 한눈에 확인할 수 있습니다.

예를 들어 saturation region point B에서의 입력 전압 v(GS)는

saturation 전류 식과 회로의 v(DS)에 대한 식을 연립하여 구할 수 있습니다.

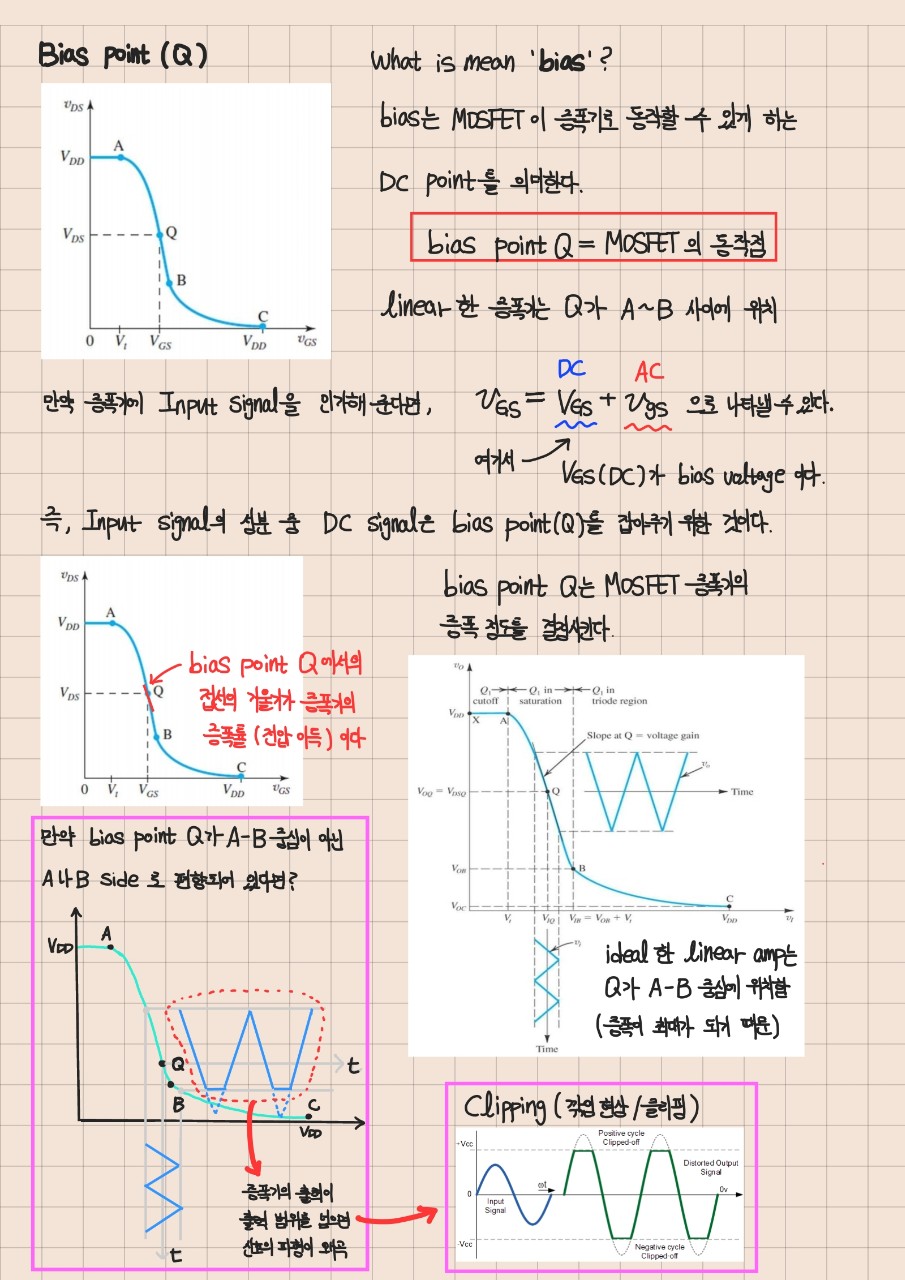

이번에는 bias에 대해서 알아보겠습니다.

일반적으로 MOSFET 소자를 사용한 실습이나 spice simulation을 하는 중에 원하는 동작을 못하는 일이 생깁니다.

대부분의 경우는 사용자가 MOSFET 소자의 bias를 모르거나 따로 정해주지 않기 때문에 발생합니다.

그만큼 MOSFET을 사용함에 있어서 bias는 무엇보다 중요한 조건입니다.

아래의 그림을 보시죠.

bias는 MOSFET amp를 동작시키는 가장 기본적인 조건입니다.

우리는 이러한 bias를 DC signal로 정해줄 수 있습니다.

우리가 증폭기에 입력시키는 신호는 DC 성분과 AC 성분이 혼합된 신호입니다.

이러한 입력 신호에서 DC 성분이 바로 MOSFET amp를 동작시키는 bias를 위한 신호로 작용하는 것 입니다.

DC 성분을 제한 나머지 AC 성분은 입력 신호로 amp에 입력되어 증폭되는 것이죠.

bias는 앞서 다루었던 VTC graph를 통해 확인 및 조정할 수 있습니다.

VTC graph에서의 bias는 Q로 표시되며 이를 bias point 또는 동작점이라고 합니다.

증폭기의 성능, 즉 입력 신호의 증폭률은 VTC graph에서 Q점에서의 접선의 기울기가 됩니다.

그리고 일반적인 linear(선형) amp에서는 Q점이 A와 B 사이에 위치합니다.

amp가 ideal 하다면 동작점 Q는 A-B 정 중앙에 위치할 것이며, 이 때의 증폭률은 최대가 될 것 입니다.

그렇다면 왜 중앙일까요?

만약 동작점 Q가 B point 쪽으로 편향되어 있다고 생각해 봅시다.

(위의 오른쪽 그림을 참고해서 보시면 이해가 쉬울 겁니다)

입력 신호는 VTC graph를 통해 출력 신호로 변환하여 그려볼 수 있습니다.

그러면 그림과 같이 증폭된 출력 신호의 아래부분이 깎인 것을 볼 수 있습니다.

이러한 현상을 clipping 이라고 하며

이는 증폭기가 허용할 수 있는 출력 범위를 넘어선 신호가 일정 부분이 깎여 출력이 되는 현상을 의미합니다.

이렇듯 동작점 Q가 A나 B side로 편향되어 있다면 출력 신호가 온전한 형태를 띠지 못하고 일정 부분이 왜곡됩니다.

우리는 이러한 clipping 현상을 방지하고 출력을 최대로 뽑을 수 있게 하기 위해

동작점 Q를 가능한 한에서 A-B center에 위치시켜야 하는 것 입니다.

그렇다면 bias를 알아보았으니

CS amp를 본격적으로 분석해 보겠습니다.

앞서 amp의 입력 신호는 DC 성분과 AC 성분을 포함한다고 말씀드렸었습니다.

그렇다면 입력 신호 v(GS)를 위의 식과 같이 쓸 수 있고,

이를 saturation region 에서의 전류 식에 대입하면

MOSFET에 흐르는 전류 i(D)는 위와 같이 표현할 수 있습니다.

입력 신호가 DC+AC 인 것과 같이 전류도 DC+AC의 구성으로 표현할 수 있습니다.

최종적으로 이러한 전류 식을 통해

Transconductance(트랜스컨덕턴스), Voltage gain(전압 이득), Amplifier Drain current(증폭기의 Drain 전류)를 구할 수 있습니다.

그리고 오른쪽의 그림들은 앞서 정리한 식들을 통해 나타낸

CS amp - small signal equivalent circuit의 π model과 T model 입니다.

small signal equivalent circuit(소신호 등가회로)은 기존의 회로에서 DC 성분을 가진 parameter를 제하고

AC 성분의 변화만을 관찰하는 방법입니다.

그러므로 MOSFET amp의 회로에서 입력 전압 대비 출력 전압의 비, 전압 이득을 계산하기 위해 사용합니다.

다음으로는 앞서 배운 내용들을 가지고 문제를 풀어보겠습니다.

문제 자체는 아주 간단하기 때문에 이해하시는데 어려움은 없으실 겁니다.

MOSFET amp에는 크게 3가지 종류가 있습니다.

Common Source Amplifier(CS amp,공통 소스 증폭기)

Common Gate Amplifier(CG amp,공통 게이트 증폭기)

Common Drain Amplifier/Source follower(CD amp,공통 드레인 증폭기/소스 팔로워)

이러한 증폭기들은 앞서 배웠던 MOSFET amp의 small signal equivalent circuit을 사용하여

회로의 전압 이득 및 입-출력 임피던스를 계산할 수 있습니다.

따라서 CS,CG,CD amp를 각각 Basic한 model과 Discrete한 model로 나누어 분석해 보겠습니다.

먼저 Common Source Amplifier에 대해서 알아보겠습니다.

위의 해석에서 중점으로 관찰하셔야 할 점은 바로 Source resistance R(S)의 유무에 따른 전압 이득 변화입니다.

R(S)는 Source 단자에 있는 저항을 의미하며

만약 R(S)가 존재한다면 없는 회로와 비교하여 1/[1+g(m)R(S)]만큼 전압 이득이 감소하는 결과를 보실 수 있습니다.

이렇듯 Source resistance R(S)이 전압 이득을 감소시키기 때문에 Degeneration resistor라고도 부릅니다.

π model과 T model을 사용하심에 있어서 따로 정해진 것은 없습니다. 보시기에 편한 방법을 사용하시면 됩니다.

그리고 왼쪽의 회로에서는 π model에 early resistor r(o)를 고려하였지만

오른쪽의 회로에서는 T model에 early resistor r(o)를 무시하였습니다.

원래는 π model과 같이 r(o)를 고려해야 하지만

오른쪽의 T model에서 r(o)를 고려하기에는 식이 복잡하지기 때문에 암묵적으로 무시해주는 것입니다.

basic circuit은 증폭기 자체의 기능만을 파악하기 위해 simple하게 구성한 회로라면

discrete circuit은 실제 회로에서 사용될 수 있는 회로의 구성을 나타낸 것입니다.

(즉, discrete circuit은 실제 회로에서 그 자체가 하나의 단일 소자로써 사용됩니다.)

discrete circuit 에서는 앞서 보았던 basic circuit과는 다르게

입력 및 출력 부분에 capacitor가 추가되어 있는 것을 보실 수 있습니다.

이는 입력과 출력 신호의 DC 성분과 신호의 noise를 제거하는 역할을 하는 Bypass capacitor입니다.

이러한 cap들로 인해 회로를 해석하는 것에 부담감을 느끼실 수 있으실 수도 있습니다.

하지만 걱정하지 않으셔도 괜찮습니다.

이번에 알아보는 각종 amp의 small signal equivalent circuit 해석에서는

Mid-band 에서의 해석을 사용할 것이기 때문에 이러한 bypass cap들은 전부 short시켜 주시면 됩니다.

회로에서 frequency에 따른 parameter의 변화를 적용시켜 주어야 하지만

Mid-band에서는 bypass cap이나 inherent cap들의 영향은 전부 무시할 수 있습니다.

그러므로 small signal equivalent circuit에서 전류원은 open, 정전압원은 GND, bypass cap는 short 해주시면 됩니다.

그리고

보통 amp circuit은 입력부에 입력 신호가 바로 연결 되는 것이 아닌 특정 회로를 거친 신호가 입력되는 것 입니다.

또한 출력부에도 출력 단자가 단독으로 존재하는 것이 아닌 amp의 출력 신호를 받는 특정 회로가 존재합니다.

따라서 이를 R(sig)와 R(L)로 표시해 놓은 것 입니다.

그렇기 때문에 입력 임피던스 R(in)과 입력 전압 v(in)은 R(sig) 다음으로 연결되는 element 부터 계산하며

출력 임피던스 R(o)는 부하 저항 R(L)을 제외한 저항들로 계산합니다.

하지만 출력 전압 v(o)를 계산하실 때는 부하 저항 R(L)을 포함하셔야 합니다!!

Discrete circuit도 Basic circuit과 같이 Source resistance R(S)가 존재함에 따라

전압 이득이 1/[1+g(m)R(S)]만큼 감소하는 것을 보실 수 있습니다.

Common Gate Amplifier는 CS amp와는 다르게 Gate로 입력을 인가해주지 않으며

Gate 단자가 GND(Common) 이므로

해석을 하심에 있어서 다른 시각을 요구하게 됩니다.

하지만 해석 자체는 단순함으로 이해하시기에 어려움은 없으실 것 입니다.

Common Drain Amplifier/Source follower(CD amp,공통 드레인 증폭기/소스 팔로워)는

보통 CD amp라고 부르기 보다는 Source follower라는 이름으로 많이 사용됩니다.

이러한 이름은 회로의 특성을 분석함으로 아실 수 있습니다.

전압 이득을 계산해보면 왼쪽 위와 같은 식이 나오게 됩니다.

이 때, 보통은 1/g(m) << R(L)의 조건을 만족하기 때문에 전압 이득이 대략 1에 수렴하게 됩니다.

이러한 이유로 인하여 CD amp를 Source follower라고 부릅니다.

Source follower의 discrete circuit에서 T-model에서는 r(o)를 고려했습니다.(Dain 단자가 GND 이므로 계산이 편리)

앞에서 우리는 MOSFET을 사용한 다양한 증폭기 회로를 분석해 보았습니다.

분석한 각 amp의 Voltage gain, input impadence, output impadence를 왼쪽 아래의 표로 정리하였습니다.

대부분의 MOSFET amp 부분을 공부하시는 분들은 Voltage gain만을 중점적으로 보시고

input impadence, output impadence를 크게 신경 안쓰시는 경우가 많습니다.

하지만 MOSFET amp에서 입-출력 임피던스는 전압 이득 보다도 더 중요하게 고려해야할 사항입니다.

이전에 MOSFET amp의 small signal equivalent circuit에서 입력부와 출력부는 단일적으로 연결된 것이 아닌

입력 신호를 주는 입력 회로와 amp의 출력 신호를 받는 출력 회로가 각각 존재한다고 말씀드렸었습니다.

예를 들면 오른쪽의 그림에서 Mic와 Speaker가 양쪽에 연결된 Amp로 볼 수 있습니다.

그의 바로 아래 그림은 위의 amp schematic을 자세히 표현한 것입니다.

mic에서 입력되는 신호를 V(m), mic 회로의 저항을 R(m), amp의 입력부의 저항을 R(in)이라고 하겠습니다.

그렇다면 만약 mic에서 입력되는 입력 전압인 Vm이 amp에 전부 전달되기 위해서는

R(m)에서 손실되는 전압 없이 R(in)에 대부분의 V(m)이 걸려야 합니다.

이는 전압 분배 식에 의거한 사실이며, 따라서 R(in)은 R(m)보다 월등히 커야 합니다.

또한

amp에서 증폭된 신호가 V(amp), amp의 출력부의 저항을 R(amp), amp가 출력한 신호(전압)을 받는 회로를 R(L)이라고 하겠습니다.

그렇다면 동일하게 V(amp)는 손실 없이 대부분이 R(L)에 전달되야 합니다.

따라서 R(amp)는 R(L)과 비교하여 아주 작아야 합니다.

이러한 사실을 종합해보면

ideal한 amp는 입력 신호를 100% 받고 증폭하며, 증폭된 신호의 100%를 전달하는 동작을 해야합니다.

즉, 입력 임피던스 R(in) = ∞ 이고 출력 임피던스 R(o) = 0 을 만족해야 합니다.

하지만 현실적으로 practical한 상황에서는 이러한 조건을 만족하기 힘들게 됩니다.

따라서 앞서 배운 amp circuit들을 single circuit으로 사용하는 것이 아닌

각각의 amp를 앞-뒤로 배치하여 multistage amplifier를 구성한 후 사용하는 것이 더 높은 효율을 얻을 수 있습니다.

이를 Multistage Amplifier(다단 증폭기)라고 합니다.

이러한 다단 증폭기를 연결하는 방식은 따로 알아보지는 않을 것 입니다.

하지만 이러한 방식으로 amp circuit을 사용한 다는 것을 아시면 됩니다.

이번 글에서는 MOSFET을 사용한 다양한 amplifier circuit을 알아보았습니다.

다음 글에서는 MOSFET을 사용한 다양한 회로에 대해서 알아보겠습니다.

긴 글을 봐주셔서 감사합니다.

'Electronics' 카테고리의 다른 글

| 전자회로2 ch5. MOSFET - ① MOSFET의 구조와 작동 원리 (0) | 2021.12.14 |

|---|---|

| 전자회로2 - Abstract (0) | 2021.12.13 |